小型化與高效能:先進封裝四要素以及環氧塑封料解析

Sep 11,2024 | Adhesive

什麼是先進封裝?

先進封裝是指採用先進的設計理念和集成工藝,對晶片進行封裝級重構,以有效提高系統功能密度的技術。這個術語在行業內非常熱門,英文稱為“Advanced Package”,有時也被稱為高密度先進封裝(HDAP),是當前封裝技術發展的焦點,受到整個半導體行業的重視。

可以將先進封裝的四個要素想像成城市的基礎設施:

-

晶圓(Wafer):就像城市的地基,晶圓是製造晶片的基本材料,所有的建築(晶片)都是在這個基礎上建造的。良好的地基保證了城市(晶片)的穩定性和持久性。

-

凸點(Bump):類似於城市中的橋樑,凸點是微小的連接點,負責將晶片與封裝基板連接起來,從而實現信息的順暢傳遞。

-

重新分佈層(RDL):可以比作城市的道路網絡,用於重新連接和分配信號路徑。想像城市中建築之間的通道,RDL則是這些通道,確保不同建築(晶片)之間的信息流暢。

-

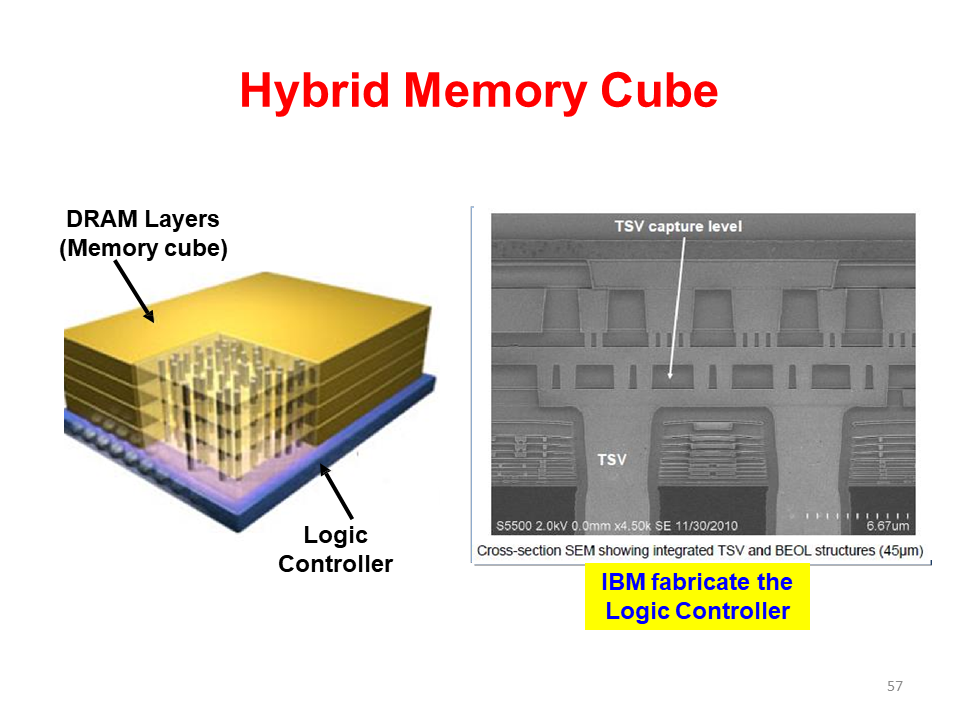

垂直互連技術(TSV):如同高層建築中的電梯,TSV是一種通過矽片垂直打通的技術,使信息可以從晶片底層傳遞到上層。它提高了晶片內部的數據傳輸效率,減少了信號延遲,就像電梯讓你快速上下樓一樣。

通過這些要素,先進封裝技術能夠大幅提升晶片的性能和功能,為半導體行業帶來新的發展機遇。

下圖展示了先進封裝四大要素的關係:RDL 負責在平面上擴展電路,TSV 實現Z 軸上的垂直電氣互連,Bump 連接晶片和封裝介面,而Wafer 則作為集成電路的基礎載體,接下來將分別對這四大要素進行詳細介紹。

Wafer

Wafer(晶圓)是半導體產業的核心基礎材料,作為製造積體電路(IC)的平台,可以看作是電子元件的“基石”。所有的晶片電路都在這片薄薄的矽片上進行加工和形成,每個晶片(Die)都是從Wafer上切割下來的。因此,Wafer的品質和尺寸直接影響最終晶片的性能和良率。

.jpeg?w=275&h=183)

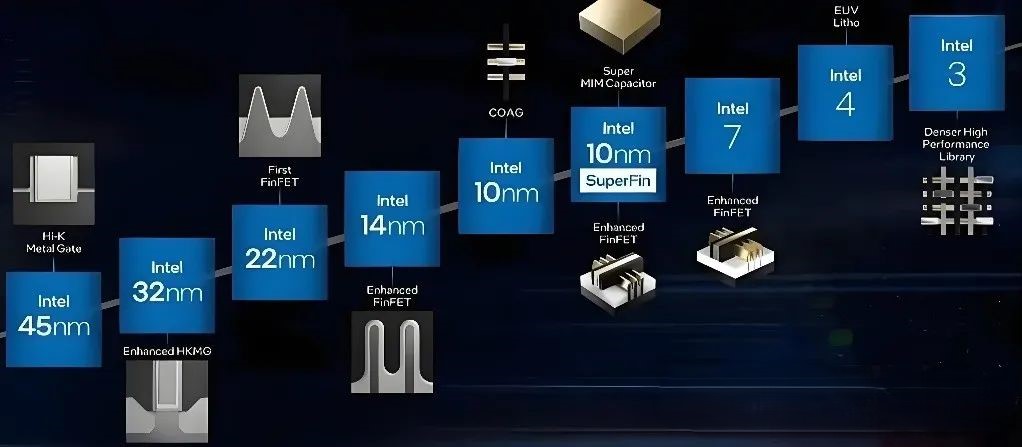

半導體Wafer的發展始於1950年代,當時首批晶圓使用鍺材料。然而,隨著技術進步,矽逐漸取代鍺成為主要的半導體材料,因為其擁有優異的半導體特性、豐富的資源及相對容易加工的優勢。

隨著製程的進步,Wafer的尺寸(直徑)不斷擴大。常見的尺寸有1英寸(25毫米)、2英寸(51毫米)、3英寸(76毫米)、4英寸(100毫米)、4.9英寸(125毫米)、150毫米(5.9英寸,通常稱為“6英寸”)、200毫米(7.9英寸,通常稱為“8英寸”)、300毫米(11.8英寸,通常稱為“12英寸”)和450毫米(17.7英寸)

對於Wafer的純度要求隨著晶片尺寸縮小和整合度提高而變得越來越高。現代晶圓幾乎是純矽材料,雜質含量極低(通常在十億分之一以下)。此外,晶圓的晶體結構需要極其完美,以避免在製造過程中產生缺陷。為了達成這些要求,晶圓必須在高度控制的環境下製造,涉及生長單晶矽棒、切割、拋光和清洗等一系列複雜製程。

除了傳統的矽晶圓,其他材料的晶圓也逐漸進入半導體製造領域。例如,氮化鎵(GaN)和碳化矽(SiC)等化合物半導體材料的晶圓在高頻和高功率電子裝置中得到了應用。這些材料具備矽無法比擬的優異性能,適用於5G通訊、射頻元件和電動汽車等特定高階應用場景。

Bump

在積體電路封裝中,Bump是一種微小的金屬凸點,主要用於實現晶片與封裝基板之間的電氣連接和機械固定。它的功能類似於橋樑,確保晶片與基板之間的訊號傳輸穩定,並提供必要的物理支撐。

最早的Bump技術可追溯到1960年代,IBM發明了稱為C4(Controlled Collapse Chip Connection)的技術。這一技術透過將錫鉛合金凸點置於晶片的焊盤上,然後翻轉焊接到基板上,這個過程被稱為“翻轉晶片”技術,成為現代Bump技術的前身。隨著電子產品微型化和整合度的提高,Bump技術經歷了多次材料與形態的演變。最初的錫鉛合金逐漸被環保的無鉛材料(如錫銀銅合金)取代。

電子裝置向更輕薄、更微型和更高性能進步,促使凸塊尺寸減小,精細間距愈 發重要。凸塊間距(Bump Pitch)越小,代表凸點密度增大,封裝整合度越高,難度也越來越大。產業內凸點間距正在朝著 20μm 推進,而實際上巨頭已經實現了小於 10μm 的凸點間距。如果凸點間距超過 20μm,在內部互連的技術上採用基於熱壓 鍵結(TCB)的微凸塊連接技術。

展望未來,混合鍵結(HB)銅對銅連接技術可 實現更小的凸點間距(10μm 以下)和更高的凸點密度(10000 個/mm2),並帶動帶 寬和功耗雙提升。隨著高密度晶片需求的不斷擴大帶來倒裝需求的成長,Bumping 的需求將不斷提升,相關材料需求也將不斷提升。

RDL

RDL(重佈線層,Redistribution Layer)是晶片封裝中用於重新分配電氣訊號的金屬層。它的主要功能是將晶片上的原始引腳重新佈線,以便與封裝基板或其他晶片進行更有效的電氣連接。可以將RDL類比為道路網絡,能夠將晶片的輸入/輸出(I/O)引腳從密集區域重新分佈到更大區域,實現更高效率的連接方式。

這項技術最早應用於倒裝晶片(Flip Chip)封裝中,旨在解決傳統封裝中引腳密度不足的問題。通過在晶片表面添加一層或多層金屬佈線,能夠重新分佈晶片內部的電訊號,突破傳統引腳密度的限制。早期的RDL技術主要使用簡單的單層佈線,適合低引腳數的晶片。隨著半導體製程的進步和晶片整合度的提升,RDL逐漸發展出多層佈線結構,支持更複雜的信號傳輸和更高的引腳密度。

為了滿足製程要求的提高,RDL使用的材料也從傳統的鋁和銅演變為更先進的材料組合,例如高導電性的銅和具有優異絕緣性能的聚醯亞胺(PI)或環氧樹脂(Epoxy)。這些材料的選擇直接影響RDL的導電性、機械強度和可靠性。

晶圓級金屬重佈線製程:

- 在積體電路(IC)上塗覆一層絕緣保護層,然後透過曝光顯影技術定義新的導線圖案。

- 接著利用電鍍技術製作新的金屬線路,以連接原有晶片引腳和新的凸點,從而實現晶片引腳的重新分佈。

一般情況下,重佈線層的金屬線路主要採用電鍍銅材料,根據需求,也可以在銅線路上鍍鎳金或鎳鈀金。相關的核心材料包括光阻、電鍍液、靶材和蝕刻液等。

重佈線層(RDL)在XY平面上的延伸和互連中起著關鍵作用。特別是在扇入晶圓級封裝(FIWLP)和扇出晶圓級封裝(FOWLP)等先進封裝技術中,RDL是核心製程之一,使封裝廠能夠在扇出封裝技術上與晶圓代工廠展開競爭。透過RDL,IO Pad可被製成不同類型的晶圓級封裝。在FIWLP中,凸塊全部生長在晶片上,晶片與焊盤之間的連接主要依賴RDL的金屬線,封裝後的IC尺寸幾乎與晶片面積相同。

而在FOWLP中,凸塊可以在晶片外部生長,封裝後的IC面積比晶片面積增加約1.2倍。以台積電的InFO作為2.5D先進封裝的代表,InFO在載體上使用一個或多個裸晶片,將其嵌入模塑料的重構晶圓中,並在晶圓上製造RDL互連和介電層,這個過程體現了「晶片優先」的製程。單晶片InFO提供了高數量的凸點,RDL線路從晶片區域向外延伸,形成了「扇出」拓撲結構。

未來,RDL技術在材料和製程上的創新將持續推進,可能會出現更導電、更柔韌的材料,以提高RDL的可靠性和適應性。同時,更精細的製造流程也將推動RDL技術向更高密度和更小尺寸發展。

TSV

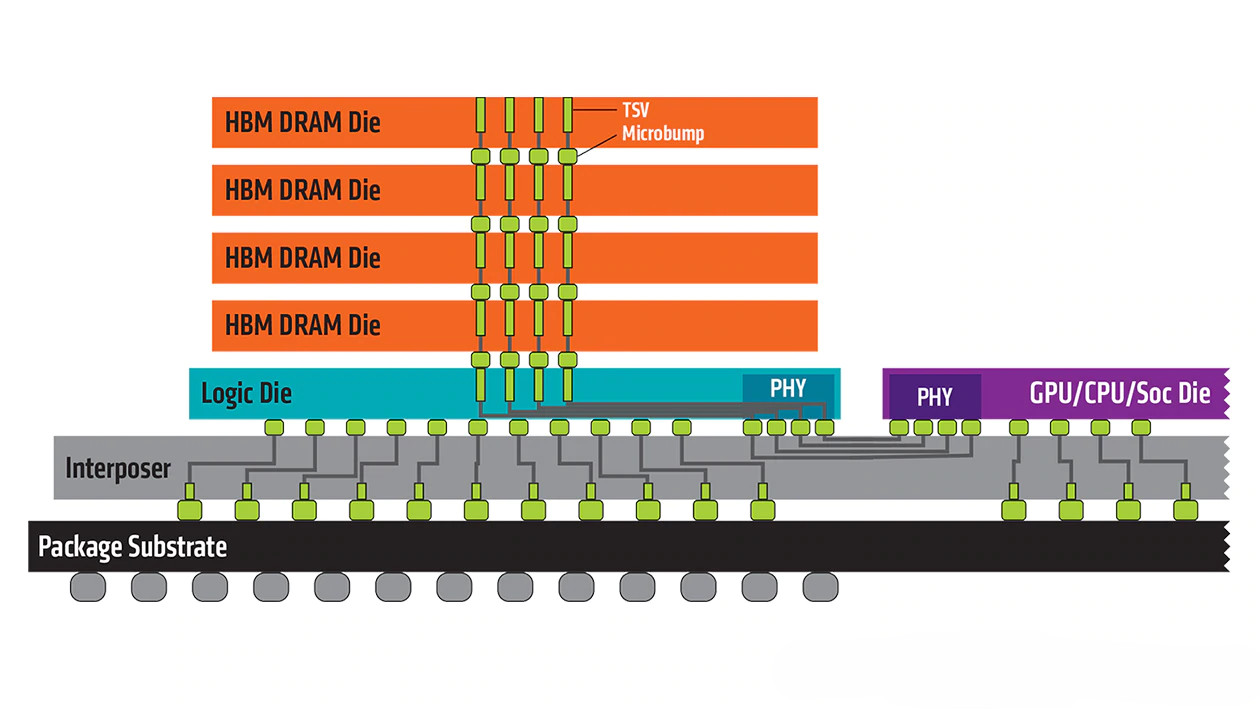

TSV技術可以分為2.5D TSV和3D晶片TSV堆疊。2.5D TSV涉及使用轉接板(Interposer)作為連接多個晶片(如處理器和記憶體)的平台。在這種架構中,晶片通過TSV在中介層上進行連接,而不是直接堆疊。可以把2.5D TSV想像成一個多層蛋糕,每層蛋糕(晶片)並不直接重疊,而是放在一個多孔的蛋糕托盤(轉接板)上,托盤的孔洞(TSV)使得各層之間可以進行訊息傳遞。

相比之下,3D TSV是一種垂直穿過矽片的電連接技術,主要用於3D積體電路(3D IC)和3D封裝。這種技術允許晶片之間進行直接的垂直連接,避免了傳統平面佈線的限制,從而實現更高的互連密度、更快的訊號傳輸速度和更低的功耗。可以想像,傳統晶片像一本厚書,每一頁必須透過書邊的紙張(外部互連)來交換信息,而TSV則像在書中打洞,使每頁能直接通過這個洞與其他頁面通訊。這種直接連接大幅縮短了訊息傳遞的距離,減少了訊號延遲和功耗。

TSV技術的概念早在20世紀80年代就被提出,但直到2000年代初期才開始受到半導體產業的廣泛關注。隨著摩爾定律的推進和晶片整合度的提升,平面製程的空間逐漸被耗盡,業界開始尋求透過垂直整合來提升性能和功能密度,TSV技術成為其中的一個重要突破。

儘管TSV技術潛力巨大,但其製程實現面臨不少挑戰,包括精確的深孔蝕刻、填充材料的選擇、熱應力管理以及孔與孔之間的電氣隔離等。為了克服這些挑戰,半導體製造商投入了大量資源進行研究與開發。如今,TSV製程已相對成熟,能夠實現高精度和高可靠性的垂直互連。

自發展以來,TSV技術在高效能運算、影像感測器和記憶體等領域取得了顯著進展。隨著製程進步和市場需求的成長,TSV的應用範圍將進一步擴大,並在未來的先進封裝技術中扮演更加重要的角色。

小結

現在針對先進封裝四大要素進行總結,四種不同的封裝關鍵點的特性如下方表格所示。

| 先進封裝關鍵要素 | 功能 | 應用 | 發展趨勢 |

| Wafer | 整合IC的載體 | 2D/2.5D/3D | 尺寸越大,精度越高 |

| Bump | 晶片介面連接 | 2D/2.5D/3D | 尺寸越小,密度越高 |

| RDL | 在平面擴展 | 2D/2.5 D/3D | 尺寸越小,密度越高 |

| TSV | 往縱向延伸 | 2.5D/3D | 尺寸越小,密度越高 |

總的來說,Wafer、Bump、RDL和TSV是先進封裝技術的四大基石,各自承擔關鍵功能。 Wafer(晶圓)作為積體電路的載體,貫穿整個半導體製造過程;Bump(凸點)則確保了晶片與基板之間的可靠連接,廣泛應用於倒裝晶片和晶圓級封裝中;RDL(重佈線層)透過重新分配晶片的電氣訊號,支援高密度和高效能的封裝;TSV(矽通孔)實現了垂直方向的電氣互連,是2.5D和3D 整合封裝的核心。四者相互配合,共同推動了晶片封裝的小型化、高密度和高性能化,並將在未來的半導體封裝技術中繼續發揮重要作用。

先進封裝技術的快速發展正在推動半導體材料需求的變化,特別是在電子封裝領域。隨著電子產品向小型化、高效能和高密度方向發展,對材料的性能要求也日益提高。在這一背景下,環氧塑封料因其優異的保護性能和電氣特性,成為不可或缺的重要材料。

環氧塑封料具有出色的耐熱性和絕緣性,能有效防止環境因素(如濕氣、灰塵和化學物質)對電子元件的損害,延長產品的使用壽命。此外,這種材料在高頻應用中表現良好,能保持穩定的電氣性能,滿足現代電子設備對信號完整性和穩定性的要求。

隨著5G、人工智慧和物聯網等新興技術的興起,對先進封裝的需求持續增長,這進一步促進了對環氧塑封料的需求。環氧塑封料的創新和改進也在不斷進行,例如開發出更輕、更薄的材料,以支持更高密度的封裝設計。

在市場競爭中,環氧塑封料的性能和可靠性將成為企業成功的關鍵因素。隨著半導體行業的不斷進步,環氧塑封料的角色將愈發重要,對於實現更高效能和更高集成度的電子產品而言,它將是不可或缺的基礎材料。

環氧塑封料

環氧塑封料以其優異的保護性能和電氣特性,成為電子封裝領域不可或缺的材料。環氧樹脂模塑膠(Epoxy Molding Compound,EMC)是一種用於封裝半導體的熱固性化學材質,其基礎成分為環氧樹脂,採用高性能酚醛樹脂作為固化劑,並融合了矽微粉等填充材料及多種助劑製備而成。其核心作用在於防護半導體晶片免受 外部環境因素(如水分、溫差、污染物等)的侵擾,並提供綜合性能如導熱、電絕 緣、抗濕性、耐壓力以及支撐等。

針對不同的下游封裝技術、應用領域及效能需求,環氧塑封料可細分為基礎類、 高效能類、先進封裝類以及其他特定應用類。基礎型環氧塑封料主要適用於TO、 DIP 等傳統封裝方式,廣泛應用於消費性電子產品和家庭電器等領域;而高性能型環氧塑封料則多用於SOD、SOT、SOP 等封裝形式,其特點為極低的應力水平、優異的黏接能力和卓越的電氣性能或高度可靠性,這類產品的主要應用領域包括消費性電子、汽車電子和新能源等。

隨著半導體晶片朝向更高的整合度和功能多樣化發展,環氧塑封料製造廠商需不 不斷開發新產品來滿足下游客戶日益增長的複雜性能需求。尤其是隨著 2.5、3D、HBM 堆疊層數的增加,對環氧塑封綜合性能要求更高。因此,針對不同世代的封裝技術, 必須客製化開發特定的產品配方,此過程涉及精細的原料選擇與配比調整。生產過程中的關鍵製程參數,如加料順序、混合溫度、混煉時間、攪拌速度等,對於不同的產品線均有所區別,導致各類環氧塑封料在物理化學性質、加工特性及最終應用效能等方面各異,業界稱為「一代封裝,一代材料」。

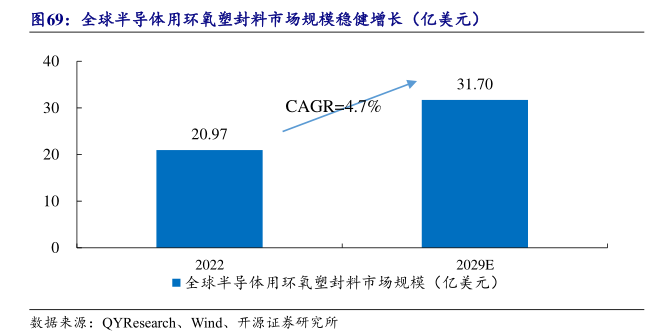

伴隨著資訊科技的持續進步以及電子產品的發展,全球半導體市場正在穩步擴大發展,從而帶動環氧塑封料的需求逐年攀升。根據QYResearch 研究團隊發布的《2023-2029 年全球半導體用環氧塑封料市場研究報告》,預計至2029 年,全球半導體用環氧塑封料的市場規模將從2022 年的20.97 億元增長至31.70 億元,期間複合年增長率CAGR 為4.7%。

.jfif?w=1280&h=1066)